BA: Evaluation der Cache-Struktur von Skylake-SP-Prozessoren

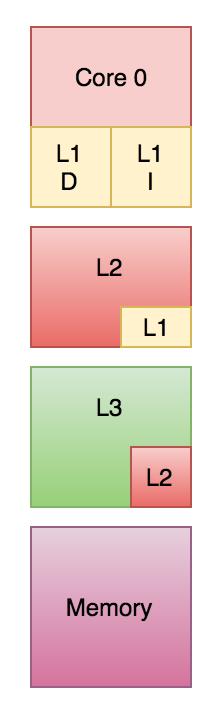

Zur Beschleunigung von Berechnungen in CPUs verfügen diese üblicherweise über schnelle Zwischenspeicher, die wiederholtes Lesen und Schreiben in den Hauptspeicher (Arbeitsspeicher) beschleunigen sollen. Diese Caches sind oft hierarchisch in Stufen oder Levels aufgebaut. In modernen CPUs ist diese Hierarchie meist inklusiv, d.h. jede weitere Stufe des Caches hält redundant die Daten der jeweils vorherigen Levels.

In den aktuellen x86-64 Architekturen von Intel ist der Level-3 (L3) Cache nicht inklusiv, d.h. Daten in L1 und L2 sind nicht zwingend im L3-Cache enthalten. In dieser Arbeit soll untersucht werden, wie sich der Cache auf diesen Architekturen auf niedriger Ebene verhält. Fragen, die sich dabei Stellen:

- Wann werden Daten in den L3-Cache verdrängt?

- Auf welchen Teil des Caches werden die Daten verdrängt?

- Erlaubt das Verhalten des Caches Rückschlüsse auf den Aufbau des Chips?

- Wie sind die Laufzeitunterschiede zwischen den einzelnen Cache-Slices?

- Hat dieser Aufbau einen direkten Einfluss auf cache-aware Algorithmen?

Zusätzliche Informationen

- Cache hierarchy

- What every programmer should know about memory by Ulrich Drepper

- Intel 64 and IA-32 Architectures Optimization Reference Manual

Voraussetzungen

Wünschenswert sind gute Kenntnisse in C oder anderen systemnahen Sprachen, aber diese können sich auch im Rahmen der Bachelorarbeit angeeignet werden.

Überblick der (möglichen) Aufgaben

- Einarbeiteung in die Details von Caches und Hardware-Countern

- Erarbeitung bzw. Identifizierung von Benchmarks und Optimierungen

- Evaluation und Interpretation der Benchmarks

Organisatorisches

- Aufgabensteller: Prof. Dr. D. Kranzlmüller

- Dauer der Bacheorarbeit: 3 Monate

- Anzahl Bearbeiter: 1

- Betreuer: Pascal Jungblut

![[PRINT]](/_images/printer1.png)