# INSTITUT FÜR INFORMATIK der Ludwig-maximilians-universität münchen

**Bachelor's Thesis**

# Evaluation of C++ SIMD Libraries

Felix Jonathan Rocke

# INSTITUT FÜR INFORMATIK der Ludwig-maximilians-universität münchen

Bachelor's Thesis

# Evaluation of C++ SIMD Libraries

Felix Jonathan Rocke

| Aufgabensteller: | Prof. Dr. Dieter Kranzlmüller        |

|------------------|--------------------------------------|

| Betreuer:        | Dr. Karl Fürlinger<br>Sergej Breiter |

| Abgabetermin:    | 27. April 2023                       |

Hiermit versichere ich, dass ich die vorliegende Bachelorarbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

München, den 27. April 2023

Telisterka . . (Unterschrift des Kandidaten)

#### Abstract

Single Instruction, Multiple Data (SIMD) units parallelize code through vectorization, thus enabling substantial performance improvements. Over the last two decades, SIMD units have become part of most CPUs. Despite this availability, many applications are not taking full advantage of SIMD units since utilizing the performance potential requires highly hardwaredependent instructions. However, the increase in performance and the substantial energy savings provided by these instructions should no longer be ignored, leading to the need for an efficient SIMD API to allow for an efficient and portable programming model.

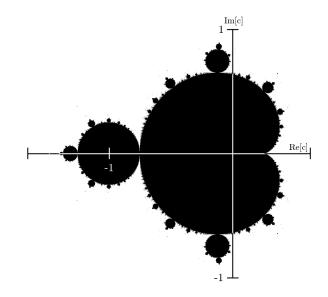

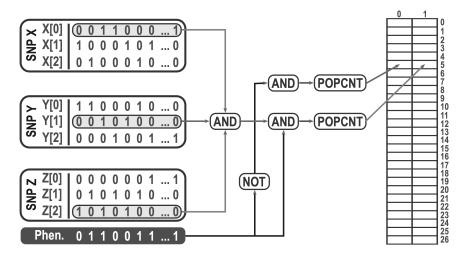

This thesis will evaluate six of the most popular SIMD libraries by reviewing their supported extensions, functions, documentation, and ease of use. Furthermore, we will benchmark the performance of the selected libraries using a floating point benchmark and compare their results to dedicated intrinsics implementations using the AVX2, AVX512, SVE, and NEON SIMD extensions. Finally, we will also take a closer look at Google's SIMD library, Highway, which has been rising in popularity recently. We will assess if the library is ready to take on complex real-world algorithms by conducting a case study on the vectorization of an algorithm operating on unsigned integers.

The results of the floating-point benchmark show that multiple libraries can match the performance of compiler intrinsics. Highway excelled with a strong performance across multiple SIMD extensions for the real-world integer algorithm. Thus, Highway may currently be the most suitable SIMD library for many software projects.

# Contents

| 2       Core SIMD Principles       3         2.1       SIMD Registers       3         2.2       Lanes       4         2.3       Memory Alignment       4         2.4       Vectorizing Loops       4         2.4       Vectorizing Loops       4         3       SIMD Programming Approaches       7         3.1       Implicit Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       7         3.2.2       Libraries       9         4       C++ SIMD Libraries       9         4.1       Library Selection Methodology       11         4.3       Selected Libraries       12         4.4       Highway       12         4.4.1       Highway       13         4.4.2       Velocic       14         4.4.3       Librindpp       14         4.4.4       NSIMD       14         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       14         4.5 <td< th=""></td<> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2       Lanes       4         2.3       Memory Alignment       4         2.4       Vectorizing Loops       4         3       SIMD Programming Approaches       7         3.1       Implicit Vectorization       7         3.1.1       Auto Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       7         3.2.1       Compiler Intrinsics       6         3.2.2       Libraries       11         4.1       Library Selection Methodology       11         4.2       Review Criteria       12         4.4       Libraries       12         4.4       Libraries       12         4.4.1       Highway       13         4.4.2       Vc       14         4.4.3       Libraries       12         4.4.4       NSIMD       13         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       16         4.4.6       Pure SIMD       16         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                          |

| 2.3       Memory Alignment       4         2.4       Vectorizing Loops       4         3       SIMD Programming Approaches       7         3.1       Implicit Vectorization       7         3.1.1       Auto Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       7         3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       9         4.1       Libraries       9         4.1       Library Selection Methodology       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       14         4.4.3       Libraries       14         4.4.4       NSIMD       15         4.4.3       Library Reviews       16         4.4.4       NSIMD       16         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       16         4.5       Review Results       20         5       Mandelbrot Benchmark       23                          |

| 2.4 Vectorizing Loops.       4         3 SIMD Programming Approaches       7         8.1 Implicit Vectorization       7         8.1.1 Auto Vectorization       7         8.1.2 OpenMP Pragmas       8         3.2 Explicit Vectorization       7         8.2.1 Compiler Intrinsics       6         8.2.2 Libraries       6         8.2.2 Libraries       11         4.1 Library Selection Methodology       11         4.2 Review Criteria       11         4.3 Selected Libraries       12         4.4.1 Highway       12         4.4.2 Vc       12         4.4.3 Libraridepp       16         4.4.4 NSIMD       17         4.4.5 SIMD Everywhere       16         4.4.6 Pure SIMD       17         4.5 Review Results       20                                                                                                                                                                                                                                                                                                               |

| 3 SIMD Programming Approaches       7         §.1 Implicit Vectorization       7         §.1.1 Auto Vectorization       7         §.1.2 OpenMP Pragmas       8         §.2 Explicit Vectorization       8         §.2.1 Compiler Intrinsics       9         §.2.2 Libraries       9         §.2.2 Libraries       9         §.2.2 Libraries       11         §.1.1 Library Selection Methodology       11         §.2.2 Review Criteria       11         §.3.3 Selected Libraries       11         §.4 C++ SIMD Libraries       11         §.4 Library Reviews       12         §.4 Library Reviews       12         §.4 Library Reviews       12         §.4 A.1 Highway       12         §.4.4.3 Library Reviews       12         §.4.4.4 NSIMD       13         §.4.4.5 SIMD Everywhere       16         §.4.4.6 Pure SIMD       17         §.4.5 Review Results       20         § Mandelbrot Benchmark       23                                                                                                                           |

| 3.1       Implicit Vectorization       7         3.1.1       Auto Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       8         3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       9         4. C++ SIMD Libraries       9         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                        |

| 3.1       Implicit Vectorization       7         3.1.1       Auto Vectorization       7         3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       8         3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       9         4. C++ SIMD Libraries       9         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                        |

| B.1.1       Auto Vectorization       7         B.1.2       OpenMP Pragmas       8         B.2.1       Compiler Intrinsics       8         B.2.1       Compiler Intrinsics       9         B.2.2       Libraries       9         A       C++ SIMD Libraries       9         A.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                     |

| 3.1.2       OpenMP Pragmas       8         3.2       Explicit Vectorization       8         3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       9         3.2.2       Libraries       9         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsindpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20                                                                                                                                                                                                                                                                                                                                                      |

| 3.2       Explicit Vectorization       8         3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       9         4       C++ SIMD Libraries       11         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2.1       Compiler Intrinsics       9         3.2.2       Libraries       11         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       16         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.2.2 Libraries       11         4. C++ SIMD Libraries       11         4.1 Library Selection Methodology       11         4.2 Review Criteria       11         4.3 Selected Libraries       12         4.4 Library Reviews       12         4.4.1 Highway       13         4.4.2 Vc       15         4.4.3 Libsimdpp       16         4.4.4 NSIMD       17         4.4.5 SIMD Everywhere       18         4.4.6 Pure SIMD       19         4.5 Review Results       20         5 Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4       C++ SIMD Libraries       11         4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1       Library Selection Methodology       11         4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2       Review Criteria       11         4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3       Selected Libraries       12         4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.4       Library Reviews       12         4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.4.1       Highway       13         4.4.2       Vc       15         4.4.3       Libsimdpp       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4.2       Vc       15         4.4.3       Libsimdpp.       16         4.4.3       Libsimdpp.       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       17         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.4.3       Libsimdpp.       16         4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.4.4       NSIMD       17         4.4.5       SIMD Everywhere       18         4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4.5       SIMD Everywhere       18         4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4.6       Pure SIMD       19         4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.5       Review Results       20         5       Mandelbrot Benchmark       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5 Mandelbrot Benchmark 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2 Pseudocode Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.3 Scalar C++ Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4 Vectorized Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.4.1 Intrinsics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.4.2 Pure SIMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.3 NSIMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $5.4.4  \text{Vc} \qquad \dots \qquad $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.5 Highway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.6 Libsimdpp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.7 SIMD Everywhere                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | Case   | e Study Vectorization of Epistasis Detection Algorithm with Highway | 3 |  |  |  |  |  |

|-----|--------|---------------------------------------------------------------------|---|--|--|--|--|--|

|     | 6.1    | Problem Introduction                                                |   |  |  |  |  |  |

|     | 6.2    | Pseudocode Implementation                                           | , |  |  |  |  |  |

|     | 6.3    | Different Population Count Approaches                               |   |  |  |  |  |  |

|     |        | 6.3.1 Pseudocode Vector Population Count with Reduction             |   |  |  |  |  |  |

|     |        | 6.3.2 AVX2 Extract Population Count                                 | • |  |  |  |  |  |

|     |        | 6.3.3 Highway Extract Population Count                              | ; |  |  |  |  |  |

|     |        | 6.3.4 AVX512 Population Count Accumulate                            |   |  |  |  |  |  |

|     |        | 6.3.5 Highway Population Count Accumulate                           |   |  |  |  |  |  |

| 7   | Eval   | uation                                                              |   |  |  |  |  |  |

|     | 7.1    | Experimental Setup                                                  | ; |  |  |  |  |  |

|     |        | 7.1.1 Hardware                                                      | ; |  |  |  |  |  |

|     |        | 7.1.2 SIMD Library Versions                                         | ; |  |  |  |  |  |

|     |        | 7.1.3 Measurement Method                                            | 2 |  |  |  |  |  |

|     | 7.2    | Mandelbrot Benchmark Evaluation                                     | 2 |  |  |  |  |  |

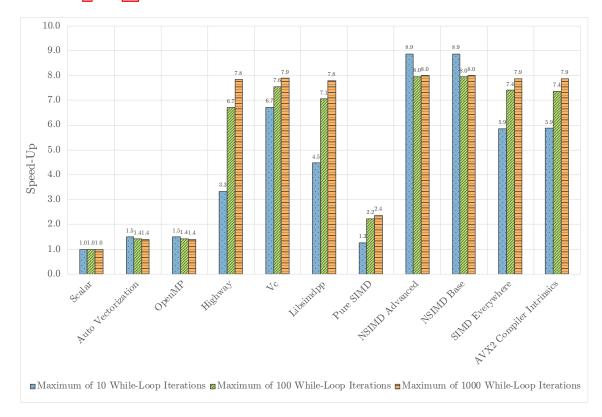

|     |        | 7.2.1 Results AVX2                                                  | 2 |  |  |  |  |  |

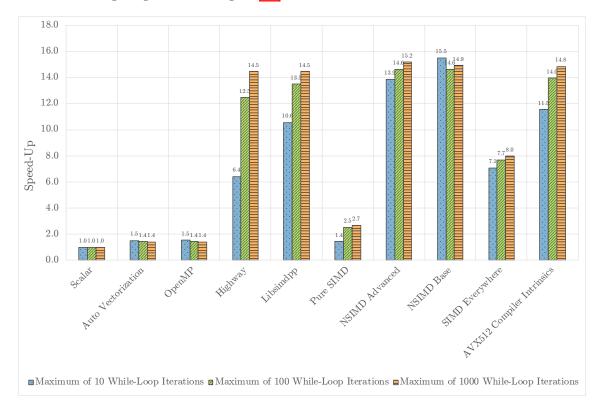

|     |        | 7.2.2 Results AVX512                                                | 4 |  |  |  |  |  |

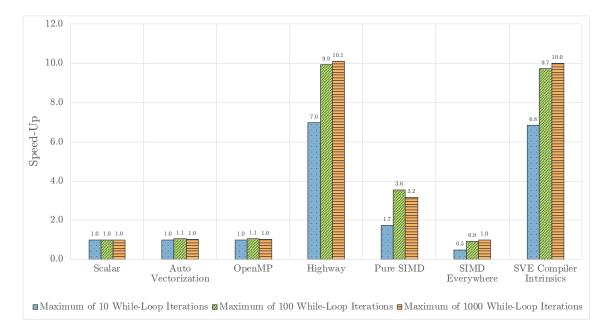

|     |        | 7.2.3 Results SVE                                                   | 2 |  |  |  |  |  |

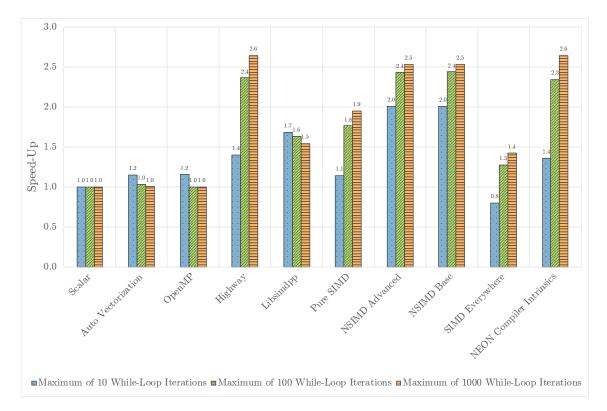

|     |        | 7.2.4 Results NEON                                                  | 2 |  |  |  |  |  |

|     | 7.3    | Case Study Epistasis Detection                                      | 2 |  |  |  |  |  |

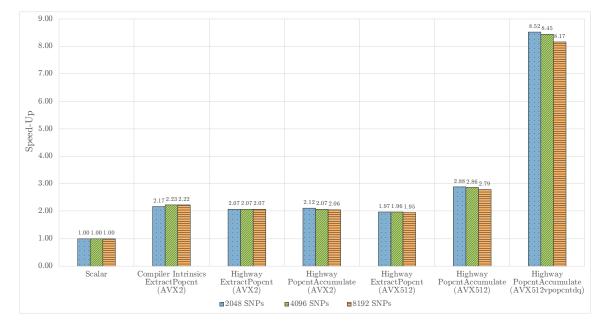

|     |        | 7.3.1 Results AVX2 and AVX512 $\ldots$                              | 2 |  |  |  |  |  |

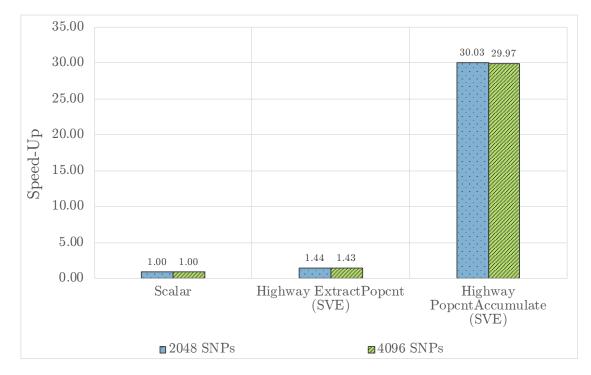

|     |        | 7.3.2 Results SVE                                                   |   |  |  |  |  |  |

| 8   | Con    | clusion                                                             | Į |  |  |  |  |  |

| Lis | st of  | Figures                                                             | Į |  |  |  |  |  |

| Lis | st of  | Listings                                                            | Ę |  |  |  |  |  |

| Lis | st of  | Tables                                                              | Į |  |  |  |  |  |

| Bi  | bliogi | raphy                                                               | ( |  |  |  |  |  |

# **1** Introduction

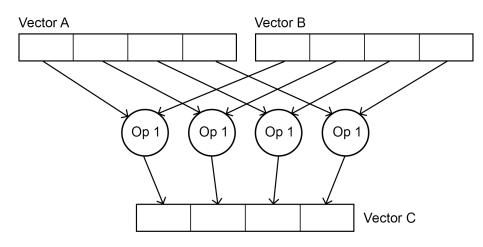

Single Instruction, Multiple Data (SIMD) units, in Flynn's classification scheme, are an internal hardware feature of most modern processors and enable a form of parallel processing Mar18. SIMD functionality was first introduced to vector supercomputers in the 1970s and then found its way into consumer processors in the 1990s. SIMD units can speed up data parallel programs through code vectorization  $[PCM^+16]$ . SIMD and vector parallelism, in general, employ the concept of Data Level Parallelism (DLP), which they achieve through data-parallel execution PCM<sup>+</sup>16, KMSZ15. In other words, SIMD instructions allow the execution of an operation on multiple data operands simultaneously instead of repeating an operation sequentially on all data points. Most vector instructions typically operate on two SIMD registers and follow the same pattern, which is visualized in Figure 1.1. First, the SIMD unit is supplied with two vectors and the operation that should be performed on them. The operation will then return the resulting vector. SIMD units typically support arithmetic, logical, and bit manipulation operations, e.g., addition, bitwise-AND, and sometimes math functions like an absolute or square root operation CFCD17, Int22a. Besides enabling better performance, employing SIMD functionality can also improve energy efficiency because only one instruction needs to be fetched for multiple data points instead of one instruction for each data point Mar18.

Figure 1.1: Visualization of a typical vector instruction operating on two vector registers with four lanes each.

SIMD extensions, such as AVX512, NEON, and SVE, are extensions to instruction set architectures (ISAs), e.g., x86, ARM, and RISC-V, which enable the use of vector operations that can lead to a substantial speed-up compared to a scalar execution. For example, the addition of two vectors with eight floating point numbers each could experience a theoretical speed-up of a factor of eight.

Besides the simultaneous operations on a vector, the memory access concept of SIMD

units may give rise to further increases in performance. Vector load and store instructions can load multiple data items from or to the memory in blocks, improving the memory bus bandwidth utilization compared to scalar load and store instructions [CFCD17]. The most significant performance improvements can be found in applications with a significant level of data parallelism. Therefore, high-performance applications, e.g., data mining or multimedia applications, often utilize vectorization. In general, computations heavily reliant on linear algebra benefit the most [Mar18]. Accordingly, for performance-critical applications, using the vector functionality of modern CPUs is highly desirable.

In order to employ the SIMD hardware of a CPU, the code needs to be vectorized first. There are several approaches to achieving this. The most common concept is to rely on the auto-vectorization features of modern compilers. The compiler recognizes data-parallel patterns and replaces the scalar arithmetic instructions with vector instructions. Although auto-vectorization has significantly improved over the last few years, compilers only achieve a fraction of the theoretically possible speed-up since they regularly fail to vectorize code with complex control flows or structured data layouts  $[PCM^+16]$ .

The best performance can often only be achieved by using intrinsic functions that directly inline assembly instructions offered by the SIMD extension while allowing for a higher level of abstraction than programming in assembly language. Unfortunately, this approach to SIMD programming requires a significant amount of effort and knowledge. Although the programmer can still think sequentially and does not need to worry about race conditions and other problems associated with parallel programming, using intrinsics is accompanied by other challenges Mar18. The most notable problems are a lack of compatibility and portability, thus requiring a different implementation for each SIMD extension. Accordingly, while being challenging and labor-intensive, intrinsics programming often results in the best performance through its low-level approach [PCM<sup>+</sup>16].

Library-based programming approaches attempt to bridge the gap between effort and performance. The functions of these libraries map to corresponding compiler intrinsics of various extensions or offer code patterns that can be vectorized by the compiler more efficiently. In this thesis, we will evaluate a variety of libraries that utilize different approaches and compare them with respect to multiple factors. Specifically, the evaluation factors will include the supported extension sets, available functions, documentation quality, ease of use, and performance. A floating point benchmark will be used for the performance evaluation. We will also examine one of the libraries more closely by conducting a case study on its ability to efficiently vectorize a real-world algorithm utilizing bitwise operations on unsigned integers.

The remaining chapters of this thesis are structured as follows. Chapter 2 will provide an in-depth explanation of SIMD's core programming principles and will introduce important terms and concepts referred to in this thesis. In Chapter 3, we will present a brief overview of the different SIMD programming approaches before more closely reviewing six different libraries in Chapter 4. Chapter 5 will present the Mandelbrot benchmark and its different implementations. Chapter 6 will describe a case study on using the Highway library to vectorize an algorithm for epistasis detection. The subsequent chapter will evaluate the results of the Mandelbrot benchmark and the case study. The final chapter will summarize the findings and give an outlook on the future of SIMD programming.

# 2 Core SIMD Principles

Since the widespread introduction of SIMD units to microprocessors in the 1990s, various extensions have been developed. The first SIMD capabilities were introduced to Intel processors with the MMX extension. Since then, Intel has developed multiple improved and more powerful extension sets [Sie16]. The integer-only MMX extension set was replaced by Streaming SIMD Extensions (SSE), which introduced vector operations on floating point numbers [Int22a]. Nowadays, the focus has transitioned away from integers toward floating point numbers [JR15].

Nevertheless, the concepts of SIMD programming remain similar across the many extensions available today. This chapter will introduce the most common terminology and the principles of SIMD programming.

## 2.1 SIMD Registers

SIMD extensions are usually implemented using SIMD units, which contain SIMD registers. These registers can store multiple values and typically have a larger size than regular registers, allowing them to hold more data. The size of vector registers has been growing over the last two decades. These registers can be found in most, if not all, modern CPUs across multiple architectures [JR15]. SIMD registers are sometimes also called vector registers. In the following chapters, these terms are used interchangeably.

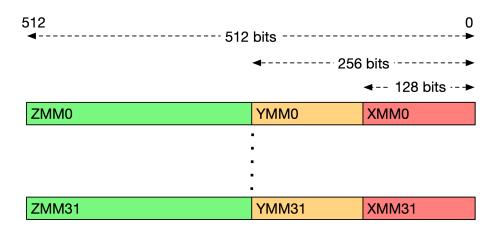

Figure 2.1: x86-64 vector registers on a CPU supporting AVX512. Visualization from Ref. Sch16.

One of Intel's most recent SIMD extensions, AVX512, has 32 vector registers, each having a size of 512-bit [Int22a, PCM<sup>+</sup>16]. These registers are addressed as ZMMO-ZMM31. Their lower half can be addressed as YMMO-YMM31 and corresponds to 256-bit vector registers introduced with AVX (compare Figure 2.1). Moreover, the lower quarter of those ZMM registers corresponds to 128-bit registers introduced with SSE [JR15], Int22a]. As a result, AVX extensions allow for backward compatibility but not forward compatibility.

## 2.2 Lanes

In SIMD registers, data is divided into multiple lanes wherein each lane holds a single scalar value. So a SIMD lane is a unit that operates on a single scalar value. The number of lanes describes how many individual scalar values fit into one vector register, i.e., how many values a vector operation can operate on simultaneously.

The number of lanes that fit in a SIMD register depends on two factors, namely, the register size and the scalar type stored in the register. For example, SSE offers 128-bit vector registers so that each register can store four 32-bit single precision floating point numbers, comparable to Figure 1.1, or two 64-bit double precision floating point numbers [PCM<sup>+</sup>16, JR15, CFCD17].

Accordingly, larger registers allow for more lanes and, therefore, more operations to be performed simultaneously, which explains the trend towards an increase in vector register sizes.

## 2.3 Memory Alignment

Operations, capable of loading and storing multiple elements in one instruction, are essential to extract the highest performance out of a SIMD unit. The fastest memory operations are possible when the array we load from or store into allows for contiguous memory accesses, and the memory address is aligned to the beginning of a cache line [CFCD17, Int23]. Thus, allowing the provided data locality to be exploited by loading entire cache lines into SIMD registers [Pac22].

While both aligned and unaligned load/store operations exist, using aligned operations is generally preferred. Operating on aligned memory improves performance because unaligned load operations can make multiple load and shift instructions necessary when a cache line is crossed to piece together the misaligned data inside a SIMD register. However, aligning memory requires additional steps, e.g., using \_\_attribute\_\_((aligned(64))), and may lead to a higher memory consumption since the data must be padded or the memory is fragmented leaving addresses unused, which can no longer be utilized effectively [Int22a] [CFCD17], [Pac22].

## 2.4 Vectorizing Loops

SIMD operations are commonly used to vectorize loops. However, for nested loops, only the innermost loop can, in most instances, be vectorized easily. Additionally, there can be no data dependence between the vector lanes because, for example, no lane can wait to read the result of another lane to finish its calculation. I.e., the calculations taking place in each lane must be independent of all the other lanes  $NDR^+11$ .

The function depicted in Listing 2.1 is a simple example of a loop vectorization, which demonstrates how a vectorized dot product could be implemented using AVX512 compiler intrinsics. To keep the example as simple as possible, we assume that the length of the vectors is a multiple of 16, which is the number of lanes available, so no extra steps are

required to handle remainders. Due to the 512-bit registers available under AVX512 and the use of 32-bit floats, the vector instructions can operate on 16 elements simultaneously. Therefore, the vectorization process can be compared with unrolling a loop, wherein each iteration, we work on 16 elements [NDR<sup>+</sup>11], [PJ15]. Thus, we increment the iterator i by the number of lanes (compare line 5 of Listing 2.1).

```

float dot_product_avx512(float * a, float * b, size_t length) {

1

assert(length % 16 == 0); // constraint for simplicity

2

3

__m512 sum = _mm512_setzero_ps();

// zero initialized vector

4

for (size_t i = 0; i < length; i += 16) {</pre>

5

__m512 av = _mm512_load_ps(a + i); // load 16 values of a into av

6

__m512 bv = _mm512_load_ps(b + i); // load 16 values of b into bv

7

sum = _mm512_fmadd_ps(av, bv, sum); // sum := (av * bv) + sum

8

}

9

10

return _mm512_reduce_add_ps(sum);

// return the sum of all 16 lanes

11

}

12

```

Listing 2.1: Dot product implementation using AVX512 compiler intrinsics.

Regarding the intrinsics used in Listing 2.1, the first one we utilized is \_mm512\_setzero\_ps, which sets every lane inside a vector register to zero (compare line 3). The C type \_\_m512 represents AVX512's 512-bit vector registers containing single-precision floating point numbers. The precision of the pack of numbers we operate on is also specified in every function through the ending of \_ps (compare, e.g., line 3), which corresponds to packed single-precision, other endings can be, for example, \_pd for packed double-precision, or \_ph for packed half-precision [Int22a]. The subsequent compiler intrinsics function we use is \_mm512\_load\_ps which loads 16 single-precision floating point numbers from aligned memory into a vector register (see lines 6 and 7). The following function, \_mm512\_fmadd\_ps, is a SIMD function requiring an additional Fused Multiply Add (FMA) unit beside the SIMD unit [Int22a]. This function can perform a multiplication and subsequent addition in a single instruction. The final function necessary for this example is \_mm512\_reduce\_add\_ps, which computes a sum across all the vector lanes and returns a scalar result (compare line 11]. It is important to note that this function consists of a sequence of instructions with narrowing vector lengths. Therefore, it should be avoided in loops to optimize performance [Int22a].

The performance of the function, dot\_product\_avx512, in Listing 2.1 could be further improved by unrolling the loop and adding multiple sum accumulators to increase the throughput. Due to the latency of 4 and throughput of 0.5 CPI of the \_mm512\_fmadd\_ps function on Intel Xeon Ice Lake-SP processors [Int22a], multiple independent accumulators can overcome the latency associated with the FMA operation through pipelining. The number of independent accumulators required for optimal performance depends on the number of FMA ports available, the latency, and the throughput associated with the FMA instruction.

# 3 SIMD Programming Approaches

Multiple programming approaches to vectorize code exist. These approaches differ in the performance they can provide, their portability, and their ease of use. This chapter will dive deeper into those approaches, examine the factors that affect their performance, and discuss their advantages and disadvantages. Furthermore, the need for SIMD libraries in vectorizing code for multiple platforms will be discussed.

## 3.1 Implicit Vectorization

The programming model of implicit vectorization refers to a technique in which the compiler or interpreter vectorizes scalar code without requiring the programmer's explicit use of vector instructions.

This approach of vectorizing code has several advantages. First, in most cases, the programmer will only be required to add compiler flags (compare Table 3.1) or pragmas to his code to enable the auto-vectorization features of modern compilers  $[PCM^{+16}]$ , [GCC22a]. This results in highly portable code since only a single version is required across all architectures because it can be compiled for all SIMD extensions and platforms, offering a compatible compiler. Therefore, it is only necessary to update the compiler to take advantage of a new SIMD extension set  $[PCM^{+16}]$ .

#### 3.1.1 Auto Vectorization

This section will focus on the auto-vectorization features of GCC (GNU Compiler Collection) compilers [GCC22b] because we used GCC's vectorizer in Section [7.2]. However, most other popular compilers, e.g., LLVM and Intel<sup>®</sup> Compiler, also have similar auto-vectorization features [LLV23, Int22b].

Work on an auto-vectorization feature for GCC started in 2003, with the primary goal being the creation of a basic vectorizer with the ability to map simple scalar operations to their corresponding vector operation. The basic vectorizer was limited to innermost loops, aligned memory, the absence of function calls, and no if-then-else constructs, besides the need for the code structure and data dependence to allow vectorization [GCC22a]. Since then, the features have been enhanced, and, for example, loops with conditions can now be vectorized in some instances. However, the mentioned restrictions still often prohibit effective vectorization [GCC22a], PJ15].

When using the vectorization feature of GCC, a few flags are of particular importance (see Table 3.1). The first and most crucial flag is -ftree-vectorize, which turns on GCC's tree vectorizer [GCC22a]. Another essential flag is -ftree-vectorizer-verbose, which outputs information on which loops were vectorized and the reason for any failed loop vectorizations. The level of detail this flag outputs can be adjusted; more information can be found in Ref. [GCC05].

| Flag                      | Description                                                                                                                                                                         |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -ftree-vectorize          | Enables vectorization, by default turned on with $-02.$                                                                                                                             |  |  |

| -ffast-math               | Required for the vectorization of most floating point<br>operations since instruction reordering can lead to dif-<br>ferent rounding errors.                                        |  |  |

| -ftree-vectorizer-verbose | Outputs information on which loops were and were not vectorized, as well as the cause. There are multiple debug levels to this flag. More information can be found in Ref. [GCC05]. |  |  |

Table 3.1: Important GCC auto-vectorization flags. Details from Refs. <u>GCC23e</u>, <u>GCC22a</u>, <u>GCC25</u>.

Although vectorization features of modern compilers have improved since their inception, they still need to catch up with explicit vectorization using intrinsics [PCM<sup>+</sup>16]. Compilers fail to vectorize code with more complex control flows because they are often limited by the information not coded into the algorithm and, therefore, cannot generate highly efficient vectorized code [KL12]. Studies have shown that auto-vectorized code, on average, only takes advantage of two vector lanes [PJ15].

#### 3.1.2 OpenMP Pragmas

More than 20 years ago, OpenMP (Open Multi-Processing) was created by compiler and hardware manufacturers to provide a more straightforward way to use threads by defining a compiler-directed threading model rather than using libraries such as Pthreads. Most popular  $C/C^{++}$  compilers support a recent version of OpenMP [Bre20, [Ope18, [PCM<sup>+</sup>16].

In Version 4.0 of OpenMP, support for SIMD was added to the API <u>Ope18</u>. Since then, the pragma **mp simd** can advise the compiler that a loop is data parallel and to vectorize it. Additional clauses can help the compiler choose safe vector lengths, inform the compiler about memory alignment and possible reductions <u>Ope18</u>, <u>Bre20</u>, <u>PCM<sup>+</sup>16</u>].

## 3.2 Explicit Vectorization

Explicit vectorization is commonly performed using compiler intrinsics or by writing assembly routines. Unfortunately, both strategies are labor-intensive due to their poor crossplatform portability [KL12]. Multiple projects attempted to solve this issue by creating highly portable and performant libraries such as the libraries in Refs. [Goo22c], Vc22a], Lib22a].

Unlike implicit vectorization, explicit vectorization requires in-depth knowledge of the principles of vectorization and mindful incorporation into the code. However, there are distinct differences in programming with intrinsics, assembly and libraries, which will be highlighted in the following two subsections.

#### 3.2.1 Compiler Intrinsics

Compiler intrinsics functions directly map to assembly instructions that are inlined by the compiler. As a result, compiler intrinsics provide one of the most performant ways of vectorizing code. In addition, intrinsics offer an abstraction layer above assembly code, facilitating use by a broader audience since only few developers are comfortable writing code in assembly language [KL12]. The GCC compiler, for example, will also further optimize code utilizing compiler intrinsics or inline assembly [GCC23b, Lir09]. Nevertheless, intrinsics have multiple drawbacks.

The first and primary reason is that intrinsics are highly hardware-dependent, making portability a significant issue. For example, AVX intrinsics lack forward compatibility, i.e., code using, for example, AVX-512 intrinsics can not be executed on older machines which, for example, support AVX2 [Int22a]. Thus, maintaining multiple versions of the same code is often necessary to ensure highly efficient execution on all machines [KL12].

Another factor is that SIMD extensions for x86 architectures do not provide complete type safety, making bugs difficult to identify <u>KL12</u>. For example, the only AVX512 type for integers is <u>\_\_m512i</u>. As a result, it is possible to, e.g., perform an addition for 64-bit integers on a vector packed with 32-bit integers without causing an error.

#### 3.2.2 Libraries

SIMD libraries address some issues known from compiler intrinsics. For example, many libraries map their functions to the underlying intrinsic functions but give them more readable names. For example, most libraries we examine offer overloaded functions so that functions have the same name across different data types, vector lengths, and SIMD extension sets. Turning functions such as the AVX function, \_mm256\_add\_ps, for the addition of single precision floating point numbers, into, for example, Add, makes the code easier to read and platform independent [Int22a], Goo22e]. This further abstraction opens up vectorization to a broader audience than intrinsics and assembly.

Another benefit of this higher level of abstraction is that the library's functions are typically mapped to various SIMD extensions. Thus, compiling the same code for different architectures and extension sets is possible, resulting in significantly more portable code since only one version of the code needs to be maintained instead of distinct versions for every extension set. However, when a new SIMD extension is released, it will be necessary to update the library.

The maintenance process is where the biggest drawback of libraries arises. In the past, research institutions or open-source projects have typically developed SIMD libraries. However, those projects have often not gained enough traction, so adding support for new SIMD extensions to the library either takes a long time or does not happen. As a result, some libraries no longer receive updates or only consider bug fixes. The problem of long-term support plagues all SIMD libraries and must be considered a significant drawback.

Nonetheless, when only considering the currently available SIMD extensions, those libraries can cut down development time considerably. Even when a new SIMD extension is released, it can take years for the corresponding hardware to become widely available. Accordingly, it is not vital for many applications to immediately support the new extension set. In the worst case, additional code versions must be maintained, while most SIMD extensions are covered by the library, which is still an improvement over not using a library.

#### 3 SIMD Programming Approaches

Most SIMD libraries that map their functions to compiler intrinsics claim to be zero overhead by utilizing the inline optimization pass of the compiler. While this may result in a zero-cost abstraction layer, there are instances in which a library implementation is slower than a compiler intrinsics implementation. Multiple factors can lead to this issue. The two most prevalent are that there still is overhead associated with the library and the other is that library functions are more limited than intrinsic ones. Therefore, combining various functions may be necessary to substitute missing functions in a library. As a result, it is sometimes possible to write a more efficient implementation utilizing intrinsics rather than a library.

# 4 C++ SIMD Libraries

This chapter will review six SIMD libraries capable of generating highly portable code, by offering an abstraction layer above intrinsics programming, as discussed in Section 3.2.2. However, we will first go over how we selected the libraries and explain the non-performance-based review criteria before examining the libraries more closely. In the final section of this chapter, we will summarize the key aspects and review the results. The performance evaluation of the libraries introduced in this chapter can be found in Chapter 7.

## 4.1 Library Selection Methodology

The libraries were selected based on three main factors. The first is popularity, the second is how advanced a library is, and the third and final factor is the design principle.

The first factor in the selection process is how popular a library is. Popular libraries frequently have more thorough documentation, tests with higher code coverage, and a larger developer community, enabling better support and assistance. We determined a library's popularity by comparing how often it is mentioned in literature and other sources. Additionally, we compared how many so-called 'stars' their GitHub pages had to gauge the following they have. Finally, we selected some of the most popular SIMD libraries currently available through this process.

Secondly, we aimed to select the most advanced libraries since they typically support more SIMD extensions, provide more features, and overall have fewer errors. Thus, they allow the programmer to develop more effective and higher-quality code. We determined how advanced a library is by reviewing the supported extensions and functions. The libraries' popularity and advancement often coincided, leading to similar choices in the selection process.

Lastly, the design principle was also essential to the selection process. For example, some libraries put simplicity first, whereas others emphasize flexibility or modularity. Furthermore, not all follow the same vectorization approach. Therefore, we included libraries with different approaches and design philosophies, even if they are less popular or advanced, to ensure we have a diverse selection to highlight the differences.

## 4.2 Review Criteria

The selected libraries' capabilities will be assessed in four main areas: supported SIMD extension sets, available functions, documentation quality, and ease of use. Performance related factors will not be considered here.

The supported SIMD extension sets are critical determinants of a library's suitability for a project since different CPU architectures support different extensions. Thus, a library supporting a wider variety will be more versatile and suitable for a more extensive range of projects. For example, a library supporting AVX and NEON can generate instructions for most modern x86 and ARM CPUs. Accordingly, the supported SIMD extensions are a critical determinant in choosing the optimal library for a project.

Besides the extensions, the available functions are equally essential in selecting a library since they must be capable of tackling the project's problems or, even better, solving any task compiler intrinsics could handle. As a result, we will review the functions of the six libraries to determine their capabilities.

Another crucial factor we consider when reviewing libraries is the quality of their documentation. They should be comprehensive, clear, fast to navigate, and easily understandable since the documentation is a tool for the developer to learn how to use the library correctly. The provided information should, for example, include the library's function signatures, usage examples, and any required dependencies.

In addition to the documentation, the ease of use is also a critical factor for consideration since a library that is difficult to use or has a steep learning curve will slow down the development process and increase the likelihood of errors. This factor is significant because the libraries should simplify SIMD programming and prevent typical errors made with compiler intrinsics. The goal of a library should be an intuitive and straightforward API that can be quickly grasped and used without a long learning period and considerable effort.

Ultimately, the four factors mentioned above can significantly impact a project's development process and overall success. Thus, we examine the six libraries based on these factors. In addition, for some libraries, we will provide supplementary relevant information.

## 4.3 Selected Libraries

In total, we carefully selected six libraries. The first four libraries for evaluation: Highway, Vc, Libsimdpp, and NSIMD, were chosen based on their popularity and advanced features. These libraries, which we consider among the most popular SIMD libraries on the market, follow a design philosophy that aims to condense the extension sets' available functions down to a subset of functions.

However, we also included SIMD Everywhere in the evaluation to ensure we examine all possible options. This library differs significantly from the previously mentioned libraries regarding its design principle since it aims to map all intrinsic functions between the SIMD extension sets. Nonetheless, the library has a substantial following and an active community working on advanced features. We also included Pure SIMD, which stood out due to its reliance on auto-vectorization, providing a unique approach different from the other libraries' principles.

## 4.4 Library Reviews

This section presents a comprehensive review of each selected library by evaluating the criteria mentioned in Section 4.2. Each library's introduction will include an analysis of the supported SIMD extensions, whereas the available functions, documentation, and ease of use are split into separate subsections. To facilitate easy comparison between the supported SIMD extensions, Table 4.1 presents an overview for each library at the time of writing.

| Library         | Supported SIMD Extensions                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Highway         | SSSE3, SSE4, AVX2, AVX-512 <sup>*</sup> , NEON, SVE, SVE2, WASM SIMD; RISC-V V                                                                                           |

| Vc              | SSE2, SSE3, SSE4.1, SSE4.2, AVX, AVX2                                                                                                                                    |

| Libsimdpp       | SSE2, SSE3, SSSE3, SSE4.1, AVX, AVX2, FMA3, FMA4, AVX512 <sup>*</sup> , NEON, NEONv2, Altivec, VSX v2.06, VSX v2.07, MSA                                                 |

| NSIMD           | SSE2, SSE4.2, AVX, AVX2, AVX512 <sup>*</sup> , NEON, SVE, VMX, VSX                                                                                                       |

| SIMD Everywhere | Full Support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, AVX, AVX2, FMA, GFNI, CLMUL, XOP, SVML, SIMD128<br>Partial Support: SSE4.2, AVX512 <sup>*</sup> , NEON, SVE, AMX, AES |

| Pure SIMD       | Dependent on compilers auto-vectorization support                                                                                                                        |

Table 4.1: Supported SIMD extension sets by each library. \*Multiple AVX512 versions are supported.

#### 4.4.1 Highway

The first library we will examine is Highway [Goo22c], a SIMD library for C++11 and above, developed by Google and distributed under an Apache 2.0 license. Development first started in 2017 and has been ongoing since with frequent updates. This library has become more popular than others before it due to the high code quality and advanced feature set. Additional information will be presented on Highway's type system, as the library will be used in a case study in Chapter 6.

The motivation behind Highway's creation is intrinsic programming's portability and compatibility struggles, which we discussed in Section 3.2.1 Highway aims to address these issues by allowing the same code to be run on various platforms and architectures, eliminating the need for multiple error-prone intrinsic implementations. As presented in Table 4.1 Highway supports the most popular SIMD extensions for x86 and ARM architectures. Therefore, offering a solid development basis. Another aim of the developers was for the library's performance not to differ more than 10% to 20% from that of a handwritten intrinsics implementation on the corresponding platform Goo22d, Goo22a.

While Highway is a promising solution to the struggles of SIMD programming, it remains to be seen if this library will be a long-term one because Google has a track record of abruptly abandoning projects Wik23.

#### Type System

The type system of compiler intrinsics for extensions, such as AVX2, is missing type safety, making bugs hard to find. However, Highway provides type safety with its numerous vector types. These numerous vector types are nonetheless easy to navigate since the library provides constructs that choose the optimal vector type for the selected datatype and current target [Goo22e].

The code in Listing 4.1 presents the most vital functions of Highway's type system, which

are usually found in the initial portion of code utilizing Highway.

```

1 const ScalableTag<T> d;

2 const size_t N = Lanes(d);

```

```

3 using V = decltype(Zero(d));

```

Listing 4.1: Essential functions in Highway's type system.